The University of Western Australia

Faculty of Engineering, Computing and Mathematics

School of Electrical, Electronic and Computer Engineering

Centre for Intelligent Information Processing Systems

# FPGA Based Embedded Stereo Vision Algorithms

# Final Year Project

David English (10225810)

Supervisors: Associate Professor Thomas Bräunl Associate Professor Anthony Zaknich

Submitted 27th October 2006

## Letter of Transmittal

David English 20 Neville Rd Dalkeith WA 6009

27<sup>th</sup> October 2006

The Dean Faculty of Engineering The University of Western Australia Nedlands WA 6009

Dear Sir,

It is with great honour that I submit this thesis entitled "FPGA Based Embedded Stereo Vision Algorithms" as partial fulfilment of the requirements for a degree of Bachelor of Engineering with Honours.

Yours Faithfully,

Maghen

David English

## ${ m Abstract}$

With improvements in technology, especially microprocessors and Field Programmable Gate Arrays (FPGA), it is possible to bring rapidly increasing levels of intelligence to autonomous robots and other embedded systems. The University of Western Australia and other research groups have need for a robotics control platform which offers traditional features such as motor and servo control alongside modern features such as fast processors, large memory, FPGAs, Bluetooth networking for control and self-organisation, as well as high speed USB interfaces for expansion. Such a platform needs to be small form factor, low power consumption and cost effective in small to medium quantities.

This project, working in a team of three, focuses on the design and verification of a new hardware platform that aims to meet all of the goals outlined, as well as accompanying software and FPGA logic designs to make the features accessible from user space under a standard embedded Linux operating system. Individually, research was also undertaken into stereo vision, with the aim of proposing an algorithm which can be made to fit this specific hardware platform, while maximising quality and performance where possible.

Significant effort has been put not only into the design of the systems presented, but also verification. Extensive testing of the timing critical components on the PCB was undertaken, and results with accompanying analysis of maximum stable speed is presented where relevant. On the logic design side, a software tool to assist in bridging the gap between traditional test bench code and VHDL designs is presented. This framework allows the rapid application of many automated test cases to logic simulations at both the behavioural and timing levels. The stereo vision research code presented includes a powerful visualisation and analysis system to assist in testing algorithms for validity and comparing against expected results.

# Acknowledgements

I would like to thank a number of people for their invaluable help during the year.

First I would like to thank my parents, for their infinite patience and support, especially after being woken up countless times by my stumbling home and into bed at early hours of the morning.

Next I would like to thank Bernard Blackham and Lixin Chin, the other members of the core design team for the M6 hardware platform and associated software and logic design. The sheer scale of the task made teamwork vital and the level of commitment and determination from all members was admirable.

I also owe a great deal to my original supervisor, Associate Professor Thomas Bräunl, who made such an exciting project available to us. His expertise, support and encouragement were vital in the difficult, early stages of the project.

Many thanks to Ivan Neubronner in the electronics workshop. I could not have possibly hoped for a more patient or knowledgeable support than he was able to offer with the manufacturing side of the project. Ivan's accumulated wisdom from previous Eyebot generations and his dedication to their support and success is astonishing.

I would also like to thank my secondary supervisor Associate Professor Anthony Zaknich for his advice in many areas, especially his encouragement to seek new and interesting results.

Thanks to Grace Choo, for not only being the second last undergraduate remaining in the Robotics Lab as the year reached its conclusion, but also for keeping me on my toes during to breaks and other potentially catastrophic moments.

Finally a very special thanks to everyone who missed out on a mention due to lack of space, I feel priviledged to have known so many great people.

# Table of Contents

| 1 | Intr  | roduction                                     | . 1 |

|---|-------|-----------------------------------------------|-----|

|   | 1.1   | Robotics, Automation and the Rise of the FPGA | . 1 |

|   | 1.2   | Embedded Vision                               | . 2 |

|   | 1.3   | Project Motivations and Objectives            | . 3 |

|   | 1.4   | Outline of Thesis                             | . 3 |

|   | 1.5   | The Eyebot M6 Feature Set                     | . 5 |

|   | 1.6   | Alternative Platforms                         | . 5 |

|   | 1.7   | Eyebot M6 FPGA Sub-System Details             | . 6 |

| 2 | FPC   | GA Image Processing Base                      | . 9 |

|   | 2.1   | M6 Platform FPGA Resources and Clocking       | . 9 |

|   | 2.2   | Component Design                              | 11  |

|   | 2.3   | FPGA Bus Arbitration                          | 11  |

|   | 2.4   | CPU Interface                                 | 13  |

|   | 2.4.  | 1 CPU Addressing                              | 14  |

|   | 2.4.5 | 2 CPU Reads                                   | 14  |

|   | 2.4.  | 3 CPU Writes                                  | 16  |

|   | 2.5   | FPGA External Memory Bus (SRAM)               | 17  |

|   | 2.5.  | 1 Controller Design                           | 17  |

|   | 2.5.  | 2 Determining Maximum Memory Clock            | 21  |

|   | 2.6   | FPGA Camera Interface                         | 23  |

| 3 | FPG   | GA Convolution Implementation                 | 25  |

|   | 3.1   | 2D Convolution                                | 25  |

|   | 3.1.3 | 1 Windowed Convolution                        | 25  |

|   | 3.1.5 | 2 Windowed Convolution Examples               | 27  |

|   | 3.2   | FPGA Implementation                           | 29  |

|   | 3.2.  | 1 Performance Results                         | 32  |

| 1 | Con   | matry of Donth Percention                     | QE  |

## FINAL YEAR PROJECT: TABLE OF CONTENTS

|   |                 | · · · · · · · · · · · · · · · · · · ·              |    |

|---|-----------------|----------------------------------------------------|----|

|   | 4.1             | Projective Geometry                                | 36 |

|   | 4.2             | Full Pinhole Camera Geometry                       | 37 |

|   | 4.3             | Epipolar Geometry                                  | 38 |

|   | 4.4             | Co-planar Images                                   | 38 |

|   | 4.5             | Practical Rectification                            | 39 |

|   | 4.5.            | 1 Affine Transform Rectification                   | 41 |

|   | 4.5.5           | 2 General Stereo Rectification                     | 42 |

| 5 | Rea             | l Time Disparity Mapping                           | 43 |

|   | 5.1             | Disparity Mapping Methods                          |    |

|   | 5.2             | Pre-Processing Filters                             | 44 |

|   | 5.3             | Choice of Match Comparison Metric                  | 46 |

|   | 5.4             | Selecting Window Size                              | 47 |

|   | 5.5             | Performance Optimisation of SAD Algorithm          | 51 |

|   | 5.5.1           | Minimisation of Search Area                        | 51 |

|   | 5.5.2           | Multiple Resolution Search                         | 52 |

|   | 5.5.3           | Reusing Earlier Results as a Lookup Table          | 52 |

|   | 5.6             | FPGA Performance Estimates                         | 53 |

| 6 | $\mathbf{Disp}$ | earity Errors                                      | 55 |

|   | 6.1             | Sub-pixel Matching                                 | 58 |

|   | 6.2             | Disparity Analysis Tool                            | 59 |

|   | 6.3             | Accuracy Improvement through Confidence Estimation | 60 |

|   | 6.4             | Applications of the Uniqueness Constraint          | 64 |

|   | 6.4.1           | Variable-Window Matching                           | 64 |

|   | 6.4.2           | Second Map Correspondence Test                     | 65 |

|   | 6.5             | Statistically Derived Method                       | 66 |

|   | 6.5.1           | Second Best Match Distance                         | 66 |

|   | <b>6.5</b> .2   | SAD Window Comparison Minimum Error Thresholding   | 66 |

|   | 6.6             | Implementation Details                             | 70 |

| 7 | Core            | rlusion                                            | 79 |

| 7.1                  | Outcomes                                  | 73 |

|----------------------|-------------------------------------------|----|

| 7.2                  | Future Work                               | 74 |

| Referen              | ıces                                      | 77 |

| A Ste                | ereo Vision Analysis Source Code Overview | 81 |

| $\mathbf{A.1}$       | Source Overview                           | 81 |

| $\mathbf{A}_{\cdot}$ | Algorithms (Native C++)                   | 82 |

| A.1                  | User Interface (Managed C++Net 2.0)       | 83 |

| A.2                  | Overview of Important Classes             | 84 |

| B Ste                | reo Vision Analysis Logs                  | 87 |

# List of Figures

| Figure 2-1 FPGA image processing internal inter-connect bus sample timing        |

|----------------------------------------------------------------------------------|

| diagram                                                                          |

| Figure 2-2 Example schematic for internal image processing bus inter-connection  |

|                                                                                  |

| Figure 2-3 Oscilloscope output for FPGA side (top) and CPU side (bottom) of      |

| buffer chip for $2mA$ (left) and $6mA$ (right) FPGA drive current strength $16$  |

| Figure 2-4 FPGA external memory system overview                                  |

| Figure 2-5 Oscilloscope output for FPGA to SRAM data pin 0                       |

| Figure 2-6 timing diagram for FPGA to SRAM transfers, back to back read and      |

| write modes                                                                      |

| Figure 3-1 Examples of edge detectors using 3x3 windowed convolutions. Source    |

| image reproduced courtesy of Lixin Chin                                          |

| Figure 3-2 2D Gaussian filter in frequency (left) and spatial (right) domains 28 |

| Figure 3-3 Noisy source image (above right) and resultant image with reduced     |

| noise and texture (right) after application of 4x4 windowed convolution          |

| Gaussian filter (above). An enlarged region (red box) helps identify the         |

| difference in noise                                                              |

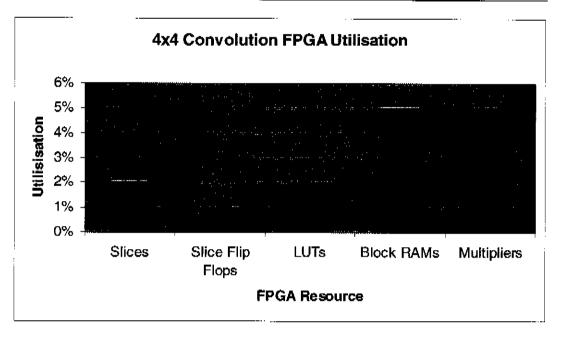

| Figure 3-4 FPGA resource utilisation for 4x4 convolution block                   |

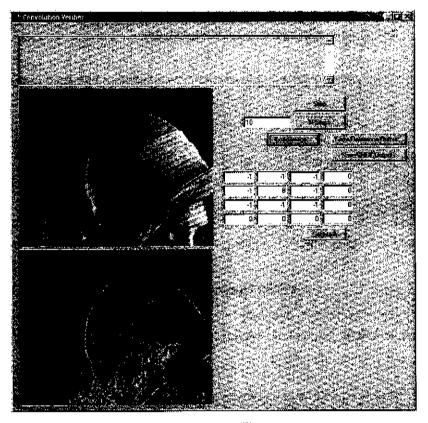

| Figure 3-5 C++ test harness with .NET UI                                         |

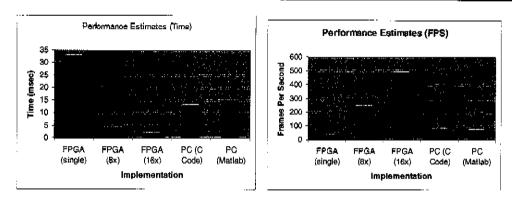

| Figure 3-6 Performance estimates for full real-time convolution system running   |

| on FPGA, with comparison to PC performance (Reference algorithm running on       |

| a 1.83GHz Intel Core Duo, binaries built with Microsoft Visual Studio 8 33       |

| Figure 4-1 Basic projective geometry[12]                                         |

| Figure 4-2 Geometry for a pair of cameras                                        |

| Figure 4-3 A comparison of the different components of relative rotation for two |

| camera images, including the depth skew from the yaw and pitch components.41     |

| Figure 5-1 Example discrete 5x5 Laplacian of Gaussian (LoG) filter[18] 45        |

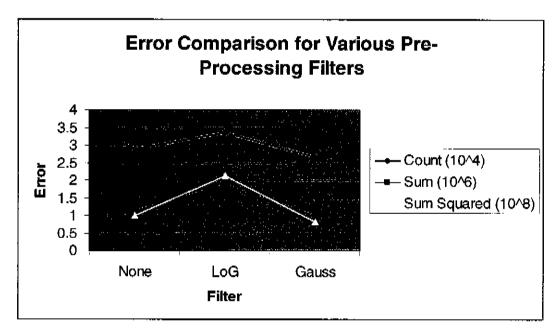

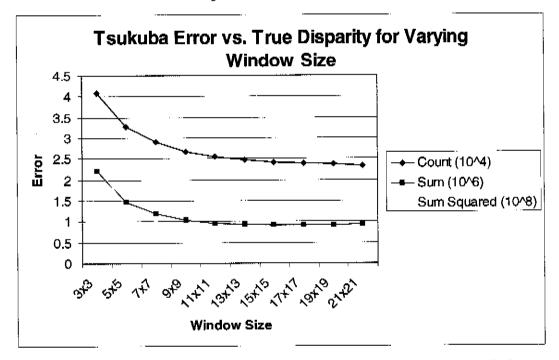

| Figure 5-2 Graphical summary of data from Table 5-1 46                                |

|---------------------------------------------------------------------------------------|

| Figure 5-3 Disparity Error for various window sizes using the plain SAI               |

| disparity method49                                                                    |

| Figure 5-4 Disparity maps and error relative to ground truth[19, 25] for basic        |

| disparity algorithm applied to Tsukuba image set at selected window sizes. $\dots$ 51 |

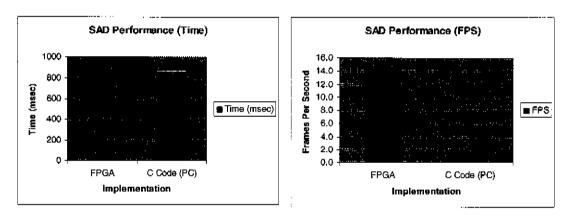

| Figure 5-5 FPGA Implementation SAD performance estimates for $50\mathrm{MHz}$ Xilinx  |

| Spartan S3E500 FPGA with 100MHz RAM compared to 1.83GHz Intel Core                    |

| Duo based PC (single thread code) with 2MB cache and $667\mathrm{MHz}$ DDR2 RAM       |

| (352x288 source image resolution, 7x7 window.)54                                      |

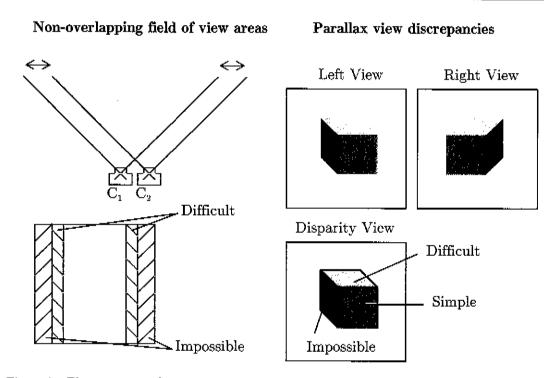

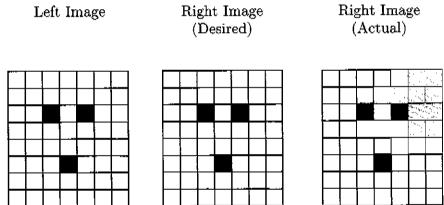

| Figure 6-1 The two types of visible area discrepancy between stereo image pairs       |

|                                                                                       |

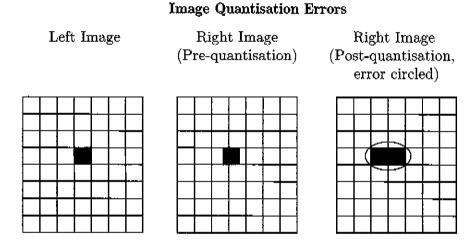

| Figure 6-2 Discrepancy in quantised sterco image windows due to sub-pixel             |

| offsets56                                                                             |

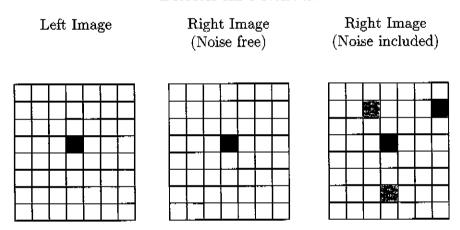

| Figure 6-3 Discrepancy in stereo image windows due to noise in detector ADC $57$      |

| Figure 6-4 Discrepancy in quantised stereo image windows due to sub-pixel             |

| offsets57                                                                             |

| Figure 6-5 7x7 window Tsukuba disparity map with example low confidence               |

| matches highlighted next to ground truth61                                            |

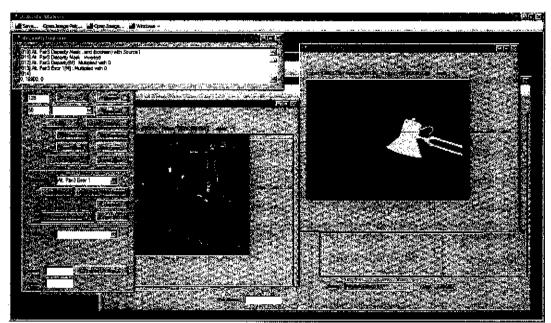

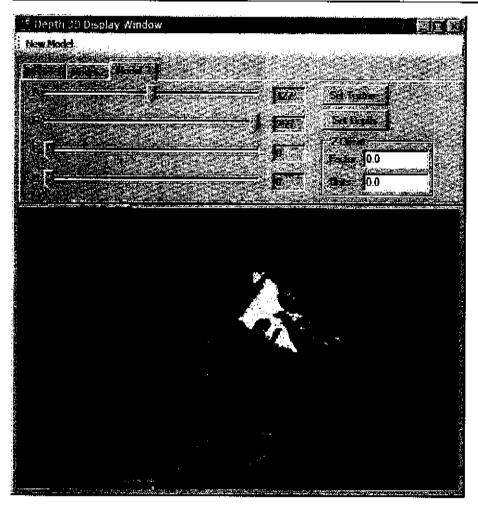

| Figure 6-6 An early build of the final disparity analysis application written in      |

| support of this project. A simultaneous cursor and detailed analysis logging can      |

| be seen in action61                                                                   |

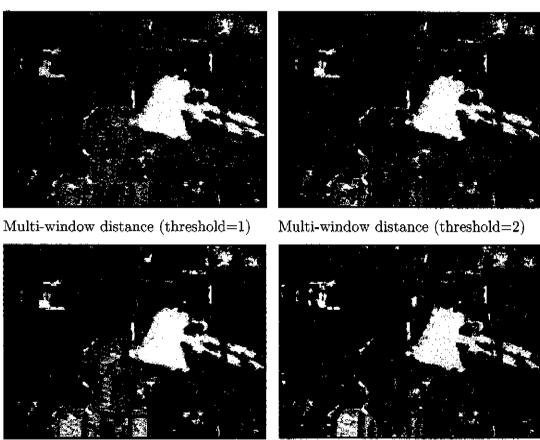

| Figure 6-7 Disparity maps with low confidence regions highlighted for various         |

| estimation techniques63                                                               |

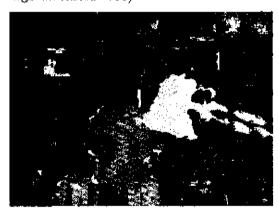

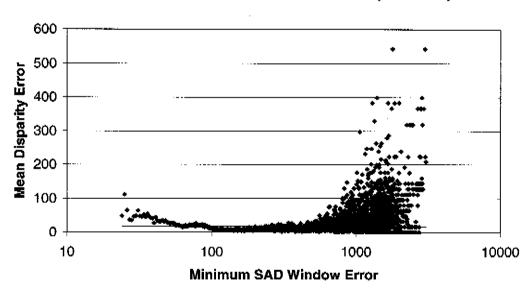

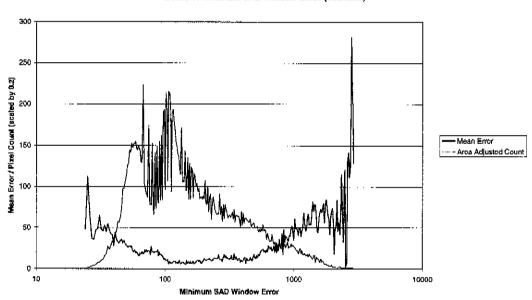

| Figure 6-8 Mean disparity error value as a function of the minimum SAD                |

| window's error value67                                                                |

| Figure 6-9 Mean error and area adjusted pixel counts as a function of the best        |

| matching SAD window's error value. Counts are adjusted so that all areas along        |

| the logarithmic graph correspond to the same amount of pixels                         |

| Figure 6-10 Plot of the adaptive moving average of SAD disparity error                |

| compared to the true disparity for different minimum SAD window error values.         |

| The adaptive moving average groups the values into equally sized bins           |

|---------------------------------------------------------------------------------|

| irrespective of the density of data points along the x-axis                     |

| Figure 6-11 3D visualisation of minimum window error threshold corrected        |

| depth map(green) as compared to original (red) and truth (grey.) Green areas    |

| represent points where the depth map was not completely fixed, while red errors |

| represent areas that are wrong in the plain disparity map but fixed after       |

| thresholding and nearest replacement                                            |

| Figure 6-12 Results of applying threshold test followed by various corrective   |

| procedures to test images                                                       |

# List of Tables

| Table 2-1 M6 Platform FPGA Resources [5].                                                      | 10           |

|------------------------------------------------------------------------------------------------|--------------|

| Table 2-2 Relative performance of bidirectional transfers                                      | 20           |

| Table 2-3 Time period variables for FPGA - SRAM bus timing                                     | 22           |

| Table 2-4 Data pin $0$ rise times and estimated $/$ experimental maximum cl                    | lock         |

| settings for the two PCBs tested                                                               | 23           |

| Table 2-5 Summary of relevant camera output pins                                               | 24           |

| Table 4-1 Stereo source images captured with a single camera moved by ha                       | ınd,         |

| along with SAD disparity map and minimum window error. It can be seen t                        | that         |

| the SAD algorithm, as discussed later, does not require perfect alignment.                     | . In         |

| particular many of the regions with poor accuracy are due to deficiencies in                   | the          |

| SAD algorithm irrespective of rectification, which will be covered in more de-                 | etail        |

| in the later chapters                                                                          | 40           |

| Table 5-1 Error compared to ground truth[19] for Tsukuba image set us                          |              |

| various pre-processing methods followed by a 7x7 SAD disparity map                             | 45           |

| Table 5-2 Results of comparing the effectiveness of different window sizes                     | on           |

| calculating the depth of the Tsukuba image pair as compared to the supp                        | $_{ m lied}$ |

| ground truth[19]                                                                               | 48           |

| Table 5-3 Comparison of selected FPGA resource / timing requirements                           | and          |

| errors incurred for different SAD window side lengths                                          | 50           |

| Table 6-1 Error compared to ground truth for Tsukuba image set for a $7\mathrm{x}7~\mathrm{S}$ | AD           |

| disparity map in the region expected to have particular difficulties $[29]$                    | 58           |

| Table 6-2 Error totals and counts of good pixels mistakenly marked as errors                   | for          |

| various confidence estimation techniques and parameters                                        | 62           |

| Table 6-3 Error totals for nearest replacement scheme revised depth maps                       | for          |

| various confidence estimation techniques and parameters                                        | 62           |

# Terminology

| ring the course of this project.                                |

|-----------------------------------------------------------------|

| entre for Intelligent Information Processing Systems A part     |

| the Department of Electrical, Electronic and Computer           |

| ngineering at the University of Western Australia               |

| eld Programmable Gate Array – A chip containing large           |

| antities of reprogrammable logic with IO and other              |

| pabilities                                                      |

| ım of Absolute Differences – The combined difference of each    |

| ir of values sharing the same location in each of two           |

| mparison windows.                                               |

| ım of Absolute Squared Difference – Similar to SAD but the      |

| fference of each pair of values is squared before the           |

| mmation                                                         |

| nalog to Digital Converter – Using inside a camera chip to      |

| nvert the analog signal generated by light hitting each         |

| oto-detector into a binary digital signal.                      |

| atic Random Access Memory – High performance, low               |

| nsity (high cost) usually clock synchronous memory which        |

| es not require refresh periods and is usually capable of multi- |

| rt access.                                                      |

| nchronous Dynamic Random Access Memory – Lower                  |

| rformance, higher density, completely clock synchronous         |

| emory.                                                          |

|                                                                 |

# Variable Table

| X                          | 3D coordinate components (Horizontal)                           |  |

|----------------------------|-----------------------------------------------------------------|--|

| Y                          | (Vertical)                                                      |  |

| Z                          | (Depth)                                                         |  |

| U                          | 2D image coordinate components (Horizontal) /                   |  |

|                            | 2D frequency component                                          |  |

| V                          | 2D image coordinate components (Vertical) /                     |  |

|                            | 2D frequency component                                          |  |

| K                          | Camera Projection Matrix (intrinsic parameters)                 |  |

| T                          | Camera Transformation Matrix (simple extrinsic parameters)      |  |

| С                          | Camera Calibration Matrix                                       |  |

| $\mathbf{P}_{	ext{bidir}}$ | Performance of fully loaded interleaved bi-directional data     |  |

|                            | transfers                                                       |  |

| ${ m P_{unidir}}$          | Performance of fully loaded uni-directional data transfers      |  |

| $N_{ m batch}$             | Number of items transferred before a change of direction occurs |  |

|                            | under full bi-directional load.                                 |  |

# Chapter 1

## Introduction

#### 1.1 Robotics, Automation and the Rise of the FPGA

As computing power has grown and cost has decreased, robots and other automation machinery have increasingly replaced human labour and supervision required for manufacturing and other repetitive tasks. Similar automated intelligence can play an active safety role, for instance in cars. Often automated systems are only viable if they are reasonably priced, fit modest dimensions and do not consume excessive amounts of power. Since the dawn of microprocessors, which pack many transistors onto a small area, the problem for most systems has not been size of the electronics, but power consumption and the size, cost and or weight of the supply required. In modern times, with chips consisting of tens of millions of transistors becoming cheap and requiring only a few square centimetres of area on a circuit board, this problem has only exacerbated.

Increasing on chip transistor counts have allowed general purpose processing architectures to grow in performance. Usually, with more complex designs this performance gain is much smaller than the increase in power consumption. For instance, a wider issue on a super-scalar processing grows the power consumption per instruction[1]. A slightly less power hungry approach is to go for multiple, seperate cores or larger cache sizes. Still dedicated logic, because it can be designed to perform many fixed steps with each clock cycle, can gain much greater performance to power and performance to transistor count ratios.

It accomplishes this by removing unnecessary operations, having no instruction decoding and no execution tracking and automated fetch and cache management. On suitable tasks dedicated logic can still achieve greater parallelism combined with lower clock speeds to realise the same or better throughput as a general purpose CPU. Despite this, dedicated logic is still used for very few tasks due to the difficulties in design and testing of such logic, and the very high costs of manufacture in small quantities. Recently the decrease in costs of large transistor counts has made Field Programmable Gate Arrays (FPGAs) become competitive, offering a good middle ground between software and true hardwired designs. They have dedicated logic to perform certain tasks, and vast arrays of reconfigurable (through programming) logic to perform any task with power efficiency not far behind dedicated logic. This means FPGA designs can bring high end computing performance to cost and power conscious embedded systems.

#### 1.2 Embedded Vision

Computer vision is the body of theory related to the processing of images by computational systems. Image data is two dimensional, and modern cameras will produce pixels with hundreds of thousands or even millions of pixels at video frame rates. Performing processing tasks on such data sets can involve high orders of complexity, especially for advanced procedures such as stereo vision depth recovery. Getting such tasks to run in real-time poses a challenge even to high end PCs, for embedded systems they have traditionally been out of the question.

As covered in the previous section, advances in technology to aid processing performance, but dedicated logic will always be superior for most tasks. Computer vision tasks in particular tend to have high degrees of exploitable parallelism and repetitiveness, because of their large input data sets. Using

FPGAs to implement algorithms with low power consumption and low cost cost in small to medium quantities is therefore a rapidly growing area of research.

### 1.3 Project Motivations and Objectives

The University of Western Australia and other research institutions are developing autonomous robots which can perceive and interact with the world. This project aims to provide a base computing platform which can serve as the nerve centre for these robots.

The specific objectives of this project were to:

- Design a major overhaul of the ageing Eyebot platform with modern computational power and expanded IO

- Maintain an affordable price in small quantity production

- Maintain a small form factor and low power consumption

- Utilise an FPGA to maximize IO capabilities and image processing performance

- Implement stereo vision to give robots utilising the new platform depth perception

#### 1.4 Outline of Thesis

Since the overall project began at the same time as this thesis project, the work performed included selection, sourcing, design and testing of hardware in collaboration with a team of other CHPS students. The development of the FPGA logic and software for the board were at many points stalled by the hardware development. Therefore this thesis focuses on the following areas of work performed:

- Design and implementation of the FPGA logic and software testing frameworks required for development of FPGA enhanced image processing algorithms on the M6 platform. This includes the development and verification of: an internal memory bus, communication with external cache memory, communication with the main CPU on the board, and communication with the cameras.

- Development and testing of FPGA logic for a two-dimensional windowed convolution algorithm. The windowed convolution is a common, multipurpose tool in image processing. The implementation of this algorithm helped in determining the requirements of the FPGA internal processing layout, and also serves as a guide to the resource utilisation and performance of image processing constructs within the FPGA. The results of the latter will be important in evaluating the suitability of other, more complex algorithms before extensive time is spent on implementation.

- Development of code to link the Xilinx ISE and other HDL simulators to C code. This can be used to evaluate circuit results on the fly during logic level simulation, aiding debugging and verification of current and future image processing designs.

- Research, analysis, implementation and evaluation of software stereo

vision algorithms with the aim of creating a correct reference algorithm

which is suitable to FPGA implementation. An algorithm will be

proposed for implementation based on its quality, performance and

feasible resource requirements within the context of the M6 platform.

### 1.5 The Eyebot M6 Feature Set

The new Eyebot M6 is designed to be a vision processing platform. To this end significant computation processing power has been included. For general purpose calculations there is a 400MHz XScale processor, 64mb of SD-RAM, 16MB of flash. This processor runs Linux 2.6 and forms the basic user space programming area for the board. A Spartan 3E FPGA with attached 1MB SRAM provides space for the implementation of dedicated vision processing acceleration logic.

The Eyebot M6 IO is mostly a super set of the original Eyebot functionality. The new features that can be found include onboard USB slave and host ports, 10/100mbit Ethernet and Bluetooth for better expansion and communications capabilties. In addition four motors are now supported, and all motors, servos, PSDs, infrared ports, serial ports and other peripherals can be used simultaneously. The ability to connect two cameras to the FPGA is provided. These cameras are oriented to face the same direction and have modest spacing to aide stereo vision processing.

There have been few compromises with respect to reproducing the old system's functionality. The number of user analogue inputs has been reduced from 5 to 3. This is not anticipated to be a problem as analogue inputs can now be added in any desired quantity via USB connections. The new CPU is not binary compatible with the original Eyebot, but it will be possible to provide almost perfect backwards compatibility to C code through a port of the standard RoBIOS libraries, similar to how EyeSim current operates. This will allow existing applications to be modified only where they need to take advantage of the new functionality.

#### 1.6 Alternative Platforms

The updated Eyebot M6 developed during the course of this project is broadly similar in concept to the Balloon Board[2] developed jointly by the University of Cambridge and MIT. Although this board has been released during the course of the project, it does not meet all the objectives of the M6 project. Whilst most immediate is the lack of onboard Ethernet and Bluetooth networking, a potentially more serious disadvantage is the lack of dedicated FPGA to camera connectors. Without this the vision processing potential of the board is hampered greatly.

### 1.7 Eyebot M6 FPGA Sub-System Details

This FPGA is a Xilinx Spartan3E 500 that saw commercial release during the year this project was undertaken. At the time of its release, the Spartan3E series was manufactured in the most up to date process of any FPGA (90nm) and offered the maximum logic to dollar ratio of any suitably sized FPGA available. The Spartan 3E differs from the Spartan3s of the same packaging in that it offers more logic slices, Block RAM, hardware multipliers and input pins for the same packaging. The disadvantage is mainly that it has less power pins, and is therefore not capable of as high a total simultaneous drive current on its output pins. Since all inputs and outputs from the FPGA in the M6 platform are logic level, this disadvantage is not considered important. The additional internal resources and input pins, on the other hand, are important as they allow more features than would be possible with the best Spartan3.

A comparison between the selected FPGA and non-Xilinx FPGAs is available in [3]. A very strong argument in favour of the Xilinx part for image processing was the largest amount of internal memory. For the other functions of the platform, the high IO count available in a non-BGA was an important consideration. For all applications the maturity of Xilinx's free HDL development environment was an important factor.

One of the key intentions of the new hardware platform is to utilise the FPGA to not only provide more IO than is possible from the CPU, but also to offload many processing tasks to improve system performance. These tasks can be divided into two categories. The interrupting tasks involve little computation, but would need to interrupt the CPU often. This would cause a significant performance penalty through inefficiency introduced by switching contexts. The offloading of these tasks to the FPGA on the Eyebot M6 platform is covered in [3]. The other category of processing task that can be offloaded is image processing. Computer vision systems typically require highly repetitive operations performed across large 2D data sets. These tasks are often ideally suited to offloading to the FPGA as the FPGA is at its most efficient when performing tasks repetitively, and has multiple cache RAM blocks which can all be accessed simultaneously to achieve much higher bandwidth per clock than a conventional processor. On the Eyebot M6 platform the FPGA also has its own RAM, so these tasks can be performed without placing a high load on the CPU's memory bus. This is particularly important because the CPU's memory bus has to sustain the LCD refreshes, in addition to serving the software memory accesses. The rest of this thesis will describe the methods and attempts to offload processing tasks from the CPU to the FPGA on the Eyebot M6 platform. A discussion covering the offloading of different tasks on this platform can be found in [4].

# Chapter 2

# FPGA Image Processing Base

As outlined earlier, the new Eyebot M6 platform features an FPGA to extend the IO and image processing capabilities of the board. The implementation of the ground work required in support of the image processing side is covered in this chapter.

### 2.1 M6 Platform FPGA Resources and Clocking

The M6 platform features a Xilinx Spartan3E S3E500 FPGA chip in a PQ208 package. The resources available on this FPGA are summarised in Table 2-1. Utilisation figures discussed in this thesis will be as a percentage of those available in this particular FPGA. It is important to note that FPGA utilisation does not sum strictly linearly. The placement and therefore routing methods available vary as different combinations of logic components are included. Still these figures offer a rough guide which can help in estimating the feasibility of a final design before it is fully implemented.

| Feature         | Capacity                          |

|-----------------|-----------------------------------|

| Multipliers     | 20 (18bitx18bit => 36bit)         |

| Block RAM       | (1024x18bit) x 20 [360Kbit total] |

| Distributed RAM | (16x1bit) x 4672 [73Kbit total]   |

| Feature                | Capacity                      |  |

|------------------------|-------------------------------|--|

| Registers              | (1bit) x 9312 [9.1Kbit total] |  |

| Logic Slices           | 4656                          |  |

| Digital Clock Managers | 4                             |  |

Table 2-1 M6 Platform FPGA Resources [5].

The FPGA receives one external clock signal from a 50MHz oscillator, referred to internally as M6CLK. This clock speed was selected as a lowest common denominator based on experimentation with the clock period of various algorithms. Reasonable degrees of pipelining were employed at all stages to ensure practical results. A second clock which is usually between one and a half and two times faster than the main system clock is generated using a DCM. This second clock is used by the memory controller, and is referred to as MEMCLK, but is also potentially available to other logic. Extreme care must be taken when performing IO between logic of different clock speeds.

It is recommended that algorithms aim to run purely off the main clock where possible. While it is possible to generate additional clock signals with the remaining three DCMs available on the chip, the Xilinx XST synthesiser has difficulty routing circuits with complicated clocking constraints. This occurs because the FPGA is divided into clock regions, and if there are more than four clocks, the FPGA must decide which areas will receive which clocks. The additional clocks required for the cameras and memory controllers already require special care to realise a circuit with valid routing. It is therefore recommended that processing algorithms utilise only the clocks provided. Using additional clocks is likely to result in unpredictable incompatibility with other features.

### 2.2 Component Design

Developing efficient implementations of algorithms to fit an FPGA's processing model is a laborious process. It is important that each routine implemented be able to co-exist in the greater system. To this end, several small interface standards were agreed during the implementation of the first image processing routines on the FPGA. These common standards deal mainly with the method for streaming data between different routines and external memory.

One of the primary goals of the design was to componentise the FPGA logic as much as possible. It is hoped that users in the future will be able to mix and match different FPGA components within the limits of the resources available. Typically designing for an FPGA involves HDL coding which is far from intuitive. Alternative design systems that feel more like conventional procedural programming languages do exist. These alternatives still require specialist skills[6], and are often tailored very specifically to fit within a particular ecosystem such as the AMD Opteron CPU and Xilinx Virtex FPGA pairings popularised by Cray's XD-1 super-computer[7].

#### 2.3 FPGA Bus Arbitration

Individual image processing components within the FPGA need to be able to stream data to each other with the maximum practical bandwidth. Since most data sets to be processed are larger than the FPGA's entire internal memory, it is also necessary that one or both ends of this bus for each device may be connected to a buffer in the external cache memory. Furthermore, the bus must arbitrate requests so that multiple devices making simultaneous access to the external memory do not interfere with each other.

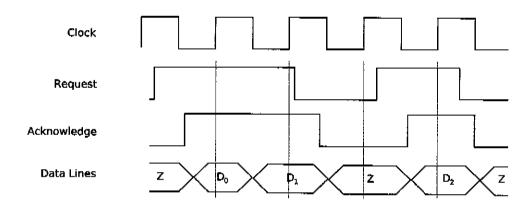

Figure 2-1 FPGA image processing internal inter-connect bus sample timing diagram

$T_0$ solve allofthese objectives in single,  $\mathbf{a}$ uniformsystem, request/acknowledge scheme was implemented with timing as shown in Figure 2-1. This underlying protocol forms the building block of all data streaming connections. The request/acknowledge scheme chosen ensures that source devices know when they need to throttle their output speed for the destination device to keep up, but does not limit transfer rate when the second device is able to process data on every clock cycle.

It is important to note that devices are meant to send their output data lines high impedance unless the host is asserting the acknowledge line. This is to allow for the use of an arbitration tree to divide up access to the memory bus. A binary tree arbitration scheme is used as propagation delay is sufficiently fast as to not slow down devices running off the main clock. The binary tree arbitration scheme is also the simplest to implement and reconfigure priority wise, as great flexibility can be achieved utilizing only the two types of arbitration blocks provided. The first, called the alternate arbiter, alternates between each of its inputs every time it gets access to the bus. The second type, called the priority arbiter, always gives priority to one of its request line, and only allows the other through when the first is idle.

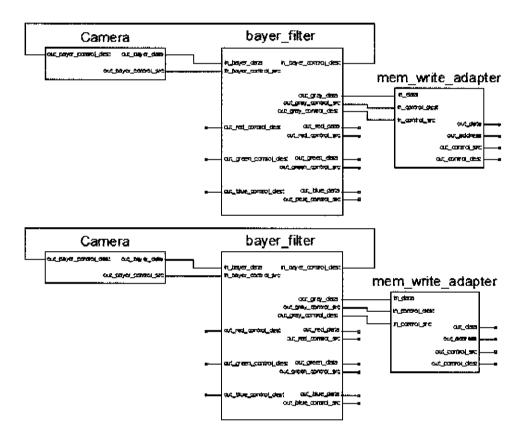

Figure 2-2 Example schematic for internal image processing bus inter-connection.

#### 2.4 CPU Interface

The centre of the Eyebot M6 platform from a user's perspective is the ARM9 CPU. It is necessary that the CPU and FPGA can reliably communicate, so the CPU can give instructions and retrieve results in a timely fashion. The discussion of CPU to FPGA communication will be split into the two separate cases of read and write. In all cases, the CPU is the bus master, and the FPGA implementation must give consideration to this and the other slaves on the PCB, holding the data pins in a high impedance state unless it is meant to be writing to the bus.

The pin layout on the initial PCB configuration required that reads be performed in VLIO mode. In addition, the ready pin was tied to a constant value making it always enabled. This meant, despite using VLIO transfers, the FPGA always had to respond in the minimum time possible. The pin limitation forcing the board to run in VLIO mode has been corrected on the latest PCB generation, and this may make even faster transfer rates possible in the future. The implementation covered below is for the always ready VLIO mode necessary on the first version of the board. The techniques described here allow the FPGA to communicate accurately on all current PCB layouts with all PXA255 bus latencies set to their lowest (fastest) settings.

#### 2.4.1 CPU Addressing

The FPGA has 20 address lines connected to the CPU bus, allowing for a 20 bit address space. The top level FPGA module carves this address space up into 32 device IDs, and each lower module is allowed to read and write through one or more of these IDs. This leaves each device with 15 bits of address space, which corresponds to a 64KB addressable region as the lowest address bit corresponds to 16 bit words.

#### 2.4.2 CPU Reads

Allowing the CPU to read data from the FPGA is the most difficult task. The CPU makes a request on the address lines, and the FPGA needs to respond by placing the appropriate information on the data lines in a timely fashion. Under minimum VLIO timing conditions (highest performance), the total response time must be, at most, four of the PXA processor's memory clock cycles[8].

Working backwards from the point where the CPU latches the data the FPGA has placed on the bus, there is a propagation delay dependent on the selected drive current between the FPGA placing data on the bus and the CPU being able to latch it. This is caused by the delay of the buffer chip (approximately 0.5ns), the rise time of the buffer chip output and the rise time of the FPGA output (the last is the only one which is drive current dependent). Since only one of these times can be altered, there is a minimum time in which the FPGA must place data on the bus early of approximately 4ns. Considering the problem from the start, the FPGA must also latch the appropriate address from the CPU on an edge, and since the address data could settle immediately after the appropriate edge has passed, a full FPGA clock period (20ns) must be allowed for the FPGA to latch the data from the time the bus settles. In addition, there is a small propagation delay for the address lines (approx. 3 ns) and a small propagation delay internally to the FPGA to send the appropriate device's bus output high impedance (negligible). This makes for a maximum total delay of approximately 27ns. This is perfectly acceptable as the period of 4 of the CPUs memory clocks is 37ns (108MHz memory bus).

A problem arises when an attempt is made to directly map FPGA Block RAM into the CPU's address space. Since both addresses and data are synchronous for Block RAM, an additional 20ns delay is introduced between the FPGA latching the address and being able to present the correct data at the output. Although this happens in parallel with the other internal FPGA delays, this still brings the total propagation delay to approximately 46ns, much greater than the 37ns maximum response time. The solution to this, as utilized in the CPU to FPGA SRAM DMA controller logic, is to latch the Block RAM addresses on the falling edge of the clock, and the data output registers on the rising edge. This is perfectly acceptable as the Block RAM is effectively now clocked at 100MHz, far below it's 200MHz maximum. It also halves the added response delay from 20ns to 10ns, bringing the total response time to a total of 36ns, just slightly faster than the 37ns required. This technique has been extensively tested

with a variety of test patterns and multiple gigabytes of data, with no errors recorded.

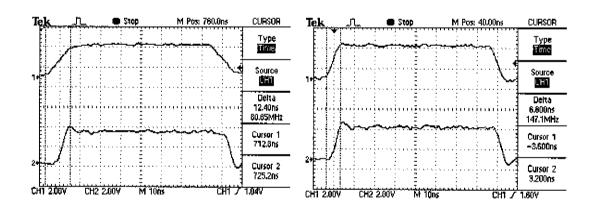

Since the PXA255 CPU is the bus master, it writes all addresses to the bus. Therefore the FPGA drive current only affects the data portion of reading on the bus. The effect of varying FPGA drive current is demonstrated in Figure 2-3. A 6mA drive current was chosen because it provided a sufficiently small delay for all tested PCBs to work flawlessly over large volumes of test data. It is possible, but unlikely that, if future FPGA images have significantly slower timing characteristics between the output data being latched internally and the same data reaching the output pins (due to a particular routing scenario), a higher drive current of up to 16mA may resolve the issue. It is preferable to keep the drive current to the minimum which does not cause errors, however, as an unnecessarily high drive current causes more interference than need be with other traces on the PCB, as well as causing more difficulties for the power supply circuitry in the form of sharper transients on the source and ground.

Figure 2-3 Oscilloscope output for FPGA side (top) and CPU side (bottom) of buffer chip for 2mA (left) and 6mA(right) FPGA drive current strength

#### 2.4.3 CPU Writes

CPU Writes present a different set of challenges from the reads. Now the data pins are driven by first the PXA255 CPU, and then the buffer, and unlike the FPGA it is not possible to adjust the drive strength of the PXA255, so it is not possible to improve the rise or fall times without PCB modifications. This is not a problem however as timing is much simpler for bus master writes. The bus master elects the address to write to, and therefore sends both address and data at the same time. The FPGA merely needs to latch both signals at any point in time where they are simultaneously valid on the bus. This is taken care of in the top level modules, and individual devices simply need to be aware that they must accept data if it is available or it will be lost (maximum of once every two FPGA clock cycles.)

### 2.5 FPGA External Memory Bus (SRAM)

The Eyebot M6 platform's FPGA is directly connected to a RAM chip. This cache memory is dedicated image processing working memory. The chip selected for this task is a single-port Static RAM (SRAM). A dual port chip was not selected, not simply because this would have increased cost, but also because it would have taken additional FPGA IO pins, and this would have required the sacrifice of other features on the board. The SRAM chip was selected over conventional Synchronous Dynamic RAM (SDRAM) for its high performance relative to the complexity of the logic required to utilize it. Unlike SDRAM, the SRAM chip does not have refresh periods and has a simple, consistent low access latency.

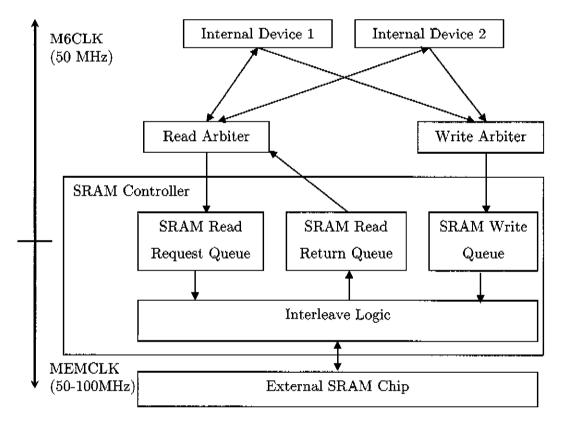

#### 2.5.1 Controller Design

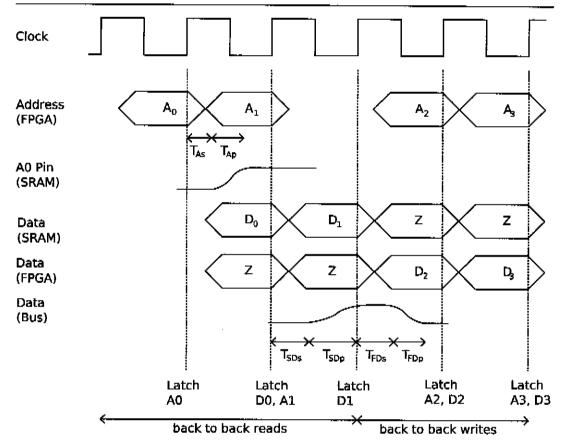

The chip selected supports back to back reads and writes at 100Mhz clock speed. There are also burst modes for compatibility with the Pentium CPU's as an external L2 cache[9]. These do not offer any bandwidth advantage compared to

the back to back modes. The back to back modes have the advantage that a completely new address can be specified for every individual read or write operation. An overview of this mode is included in Figure 2-6.

Since back to back mode is utilized, there is no need for components to make their requests in bursts. Therefore, to maximize flexibility, the bus is designed to accept all requests in units of individual SRAM data words (18 bits.) Conveniently this corresponds with the word size of the FPGA's internal SRAMs (Referred to by Xilinx as Block RAMs.) When using the SRAM's back to back mode, there is one factor that must be taken into consideration: The effect of switching between write and read mode on the bandwidth of the chip. Although a read or write can be performed every single clock cycle for unidirectional transfers, the individual reads actually take two clock cycles, one for the address and a second for the data. These cannot be overlapped with the writes as the write requires both sets of lines during the same cycle. The result is that switching from read to write mode requires a clock cycle where no new request initiates, and the result is that, alternating between read and write mode each access limits the chips to performing two memory accesses only every three clock cycles.

Figure 2-4 FPGA external memory system overview

To reduce the performance penalty, it is necessary to avoid mixing of read and write operations too often. This can be achieved by queueing both both read and write requests, and then performing each type of request in batches. The maximum bidirectional performance can be expressed thus:

$$P_{bidir} = \frac{2N_{batch}}{2N_{batch} + 1} P_{unidir}$$

(2.1)

The maximum bidirectional performance as a percentage of the common unidirectional performance for selected batch sizes is indicated in Table 2-2. There is a diminishing performance gain with increasing batch size and clearly queue sizes greater than 16 offer extremely small gains relative to additional queue size.

| Request Batch Size (N <sub>batch</sub> ) | Performance (% Unidir) |

|------------------------------------------|------------------------|

| 1                                        | 66.7%                  |

| 2                                        | 80.0%                  |

| 3          | 85.7%  |

|------------|--------|

| 4          | 88.9%  |

| 6          | 92.3%  |

| 8          | 94.1%  |

| 10         | 95.2%  |

| <b>1</b> 2 | 96.0%  |

| 14         | 96.6%  |

| 16         | 97.0%  |

| 24         | 98.0%  |

| 32         | 98.5%  |

| Infinite   | 100.0% |

Table 2-2 Relative performance of bidirectional transfers compared to unidirectional for selected batch sizes

Xilinx Core Generator offers a pre-designed, heavily customisable FIFO with a minimum queue size of 16. Although this FIFO consumes more logic than a custom solution might require, it has several advantages compared to a simpler design. One advantage of using Xilinx's solution is that it contains already heavily tested and proven code, which is very important to a logic design as faults can be difficult to diagnose. Another advantage lies in its key feature, a grey code counter connecting the two ends of the FIFO. This allows each end to run off independent clock signals without glitches. Asynchronous clocking is very useful because the two ends of the FIFO have different clock speed limitations. Whereas the algorithms in the FPGA operate on a 50Mhz clock, the SRAM chip and associated FPGA logic can operate at 100Mhz. The actual maximum memory clock can be slightly lower than 100MHz which the chips can support, depending on the PCB layout and other external factors. Even so, by combining a 50Mhz read and a 50Mhz write bus and connecting them to a near 100Mhz, single port SRAM, a pseudo dual-port arrangement is achieved. This arrangement running at 80MHz is able to achieve unidirectional transfers at the maximum 50MHz supported by the FPGA devices, while batching requests up to twelve at a time can achieve 77% of the bandwidth of a true dual-port 50MHz SRAM under worst case (full load) conditions. This is a significant improvement over a synchronous (50MHz) single port configuration which would achieve only 48% of the bandwidth of the dual port configuration. This pseudo dual port RAM offers most of the benefit of true dual port RAM, whilst saving

the cost difference for a true dual port chip, and more importantly for the small form factor design desired, a large amount of FPGA IO pins and PCB real estate.

#### 2.5.2 Determining Maximum Memory Clock

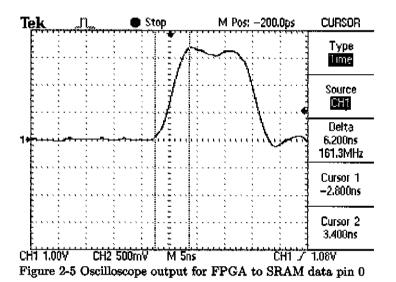

The maximum memory clock of an individual PCB can be estimated by examining the time required for the pins to change levels onoscilloscope. The output of the oscilloscope for data pin 0 on the second

PCB revision is shown in Figure 2-5. It can be observed that the measured rise time is 6.2ns. This corresponds to a frequency of 161MHz, twice the 80MHz max reliable transfer rate found for this board. Similarly, for the first PCB built the rise time was 6.0ns, which corresponds to a frequency of 167MHz, or twice the 83MHz clock speed which was the maximum stable transfer rate achieved with this board. These findings are summarized in Table 2-4.

Figure 2-6 timing diagram for FPGA to SRAM transfers, back to back read and write modes

| Period Variable             | Description                       |

|-----------------------------|-----------------------------------|

| $	extbf{T}_{	ext{As}}$      | Address set-up time               |

| ${f T}_{{f Ap}}$            | Address propagation time          |

| $\mathbf{T}_{	ext{SDs}}$    | SRAM output data set-up time      |

| $\mathbf{T}_{\mathtt{SDp}}$ | SRAM output data propagation time |

| $\mathbf{T}_{	ext{FDs}}$    | FPGA output data set-up time      |

| $\mathrm{T_{_{FD_{P}}}}$    | FPGA output data propagation time |

Table 2-3 Time period variables for FPGA - SRAM bus timing

There are two reasons the clock speed achievable is highly PCB dependent. Since the drive current for the SRAM chip cannot be altered, the rise and fall time when the FPGA reads data from the SRAM  $(T_{SDp})$  cannot be shortened by raising the current. By comparison,  $T_{FDp}$ , the equivalent transition time for the FPGA, can be shortened by raising the software configurable drive current as

necessary. The propagation of  $T_{\rm SDp}$  is the major performance bottleneck therefore, and was the signal whose rise time showed a directly proportional relationship to minimum clock period. It is important to consider that the RAM is not Double Data Rate (DDR), and therefore the clock signal has to both rise and fall during every clock period, almost twice as fast as the address and data signals. Fortunately this signal is output by the FPGA and the drive current can be raised to achieve a sufficiently fast rise and fall time. It is necessary to raise the clock drive current from the default of 2mA to at least 8mA to achieve the speeds indicated on the current board.

| PCB    | Rise time         | Est. Frequency    | Highest stable setting  |  |

|--------|-------------------|-------------------|-------------------------|--|

|        | $(\mathbf{t_r})$  | $(1/2t_r)$        | in testing (mult./div.) |  |

| First  | $6.0\mathrm{ns}$  | $81\mathrm{MHz}$  | $8/5~(80 \mathrm{MHz})$ |  |

| Second | $6.2 \mathrm{ns}$ | $83 \mathrm{MHz}$ | $5/3~(83\mathrm{MHz})$  |  |

Table 2-4 Data pin 0 rise times and estimated / experimental maximum clock settings for the two PCBs tested

### 2.6 FPGA Camera Interface

The M6 platform has been designed so that either one or two COMedia C3038 cameras may be connected to the FPGA. If two cameras are connected, the FPGA can gather data from both simultaneously. In the standard setup each camera outputs a number of signals and the FPGA is merely a passive listener. It would be possible for the FPGA to provide a common pixel clock to both cameras if their on board clocks were disabled, but the implementation discussed here is for use with unmodified cameras.

For the FPGA to receive appropriate data from the cameras, it is necessary to first program the cameras settings via an I<sup>2</sup>C bus. The details of this along with an outline of all the special considerations relating to multiple OV6630 chips on one I<sup>2</sup>C bus are available[3].

| Camera Output | Description                                                                                                     |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PCLK          | Pixel Clock – Each rising edge of this clock during a line corresponds to one pixel being available on the bus. |  |  |  |  |

|               |                                                                                                                 |  |  |  |  |

| HSYNC         | This signal is held high for exactly the duration of each                                                       |  |  |  |  |

|               | line. The falling and rising edges of this signal occur                                                         |  |  |  |  |

|               | between each line, and pixels received while this signal is                                                     |  |  |  |  |

|               | low are invalid.                                                                                                |  |  |  |  |

|               | This signal remains low during vertical blanking periods.                                                       |  |  |  |  |

| VSYNC         | This signal encodes the start of each frame as a pulse that                                                     |  |  |  |  |

|               | is longer than the period of the pixel clock. A return                                                          |  |  |  |  |

|               | low occurs before the next line begins (HSYNC goes high.                                                        |  |  |  |  |

| Y0:Y7         | The low 8 bits of the data bus are fed into the FPGA. All                                                       |  |  |  |  |

|               | pixel data is received via these lines.                                                                         |  |  |  |  |

| UV0:UV7       | The remainder of the 16 bit bus is not connected on the                                                         |  |  |  |  |

|               | M6 platform. To receive complete data it is necessary to                                                        |  |  |  |  |

|               | request an 8 bit mode from the camera (default is 16 bit.)                                                      |  |  |  |  |

Table 2-5 Summary of relevant camera output pins

Since the maximum frequency of the cameras in 8 bit mode as utilised is approximately 18MHz[10], it is unreliable to attempt to observe the PCLK signal using sampling methods. It is therefore necessary to treat this as an FPGA clock signal, and latch the outer camera pixel data registers off this. This latched data is then fed to the M6CLK circuitry using a toggle input, for which sampling is reliable. A similar technique was necessary to observe the HCLK signal with reliable relative timing to the PCLK sampling. Although it is possible to apply this technique to VSYNC, doing so results in routing problems for Xilinx's XST synthesiser. During testing the result has been that if only PCLK and HSYNC are treated as clocks, as necessary for reliability, then all devices can coexist without causing XST's clock routing to fail.

# Chapter 3

# FPGA Convolution Implementation

### 3.1 2D Convolution

The multiplication of two functions in the frequency domain is equivalent to the convolution of the functions in the time domain, and vice versa:

$$C_{x,y} = F(u,v).G(u,v)$$

(3.1)

$$c_{x,y} = f * g(x,y)$$

(3.2)

$$= \sum_{i=-\infty}^{\infty} \sum_{j=-\infty}^{\infty} f(x+i, y+j).g(i, j)$$

(3.3)

### 3.1.1 Windowed Convolution

Theoretically the calculation of the convolution value in time domain at a single (x,y) coordinate requires a sum over the entire overlapping range of the (post-translation for each step) functions. To compute the convolution for every value in an image or other data source with a mask of the same size as the image (as required for equivalence to an arbitrary frequency domain multiplication) requires an  $O(N_1^2 N_2^2)$  order calculation where  $N_1$  and  $N_2$  are the image dimensions. Defining  $M_1$  and  $M_2$  as the dimensions of the image  $N_1$  and  $N_2$  rounded up to the nearest powers of two respectively, the FFT and inverse FFT

of the data can be calculated with a computational order of  $O(M_1M_2 \cdot \log_2(M_1M_2))$ . We can also ignore the bit reversals on the FFT and inverse FFT when performing convolution via this method[11]. Clearly the basic 2D convolution is not an efficient way of performing an arbitrary frequency domain multiplication.

The windowed convolution is an optimisation which does not maintain direct equivalence with a frequency domain multiplication. It works on the principle that a function which consists entirely of zeros outside a small range of values can be computed in a much shorter time than a full convolution. The zero values themselves and the source values which multiply with the zeros in the source image do not need to be considered at each step. Therefore a windowed convolution can be computed in a complexity that is only  $O(N_1N_2.W_1W_2)$  where W<sub>1</sub> and W<sub>2</sub> are the dimensions of the window. Assuming the best case for the FFT where  $N_1=M_1$  and  $N_2=M_2$ , if  $W_1W_2$  is smaller than  $\log(M_1M_2)$  then the windowed convolution will still have a lower complexity. In practice, the window size at which the windowed convolution gains the complexity advantage is much smaller, due to its more efficient handling of non-power of two sizes. Another big advantage for an FPGA implementation is the relative simplicity of the operations in the convolution, compared to the FFT, multiply and inverse FFT alternative. This advantage is important because the implementation must be hardwired, rather than implemented in software, and therefore the logic cannot easily be reused for another task when the convolution is not taking place.

## 3.1.2 Windowed Convolution Examples

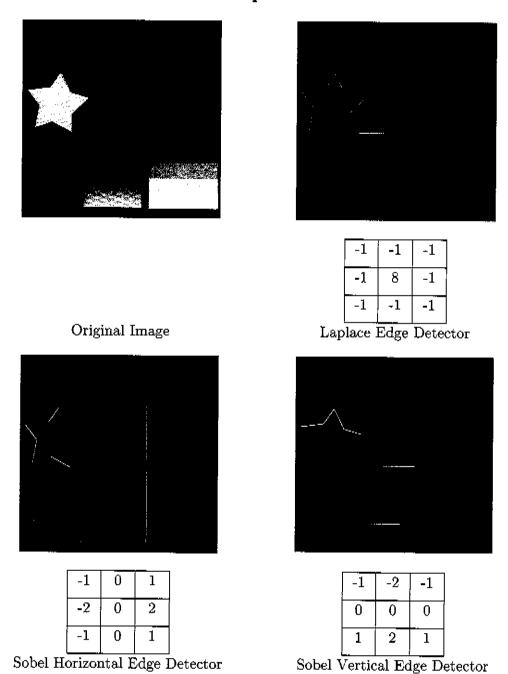

Figure 3-1 Examples of edge detectors using 3x3 windowed convolutions. Source image reproduced courtesy of Lixin Chin.

Several functions have been developed which exactly fit the windowed convolution model. Examples include the Sobel and Laplacian edge

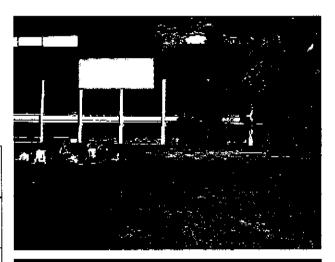

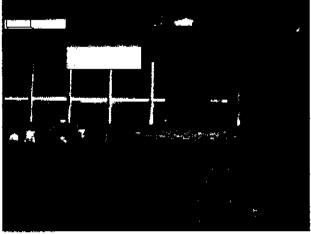

detectors(Figure 3-1), which operate a little like directional and omni-directional high pass filters respectively, but locked closely to a specific frequency range such that they tend to retain features with a dimension of a single pixel in the appropriate directions. Although only a limited number of candidate functions can be expressed exactly like this, many can be approximated adequately. A particularly common and conceptually simple example is the Gaussian low pass filter. The inverse Fourier transform (time domain) version of a 2D Gaussian function is itself a 2D Gaussian function. Gaussian functions in general tend towards zero rapidly, to a few decimal digits of precision, beyond a similar number of standard deviations away from the centre point(Figure 3-2). Therefore a very small window is often appropriate for approximating this function. It is also extremely useful in image processing, as it can be used to reduce both texture and noise from a source (Figure 3-3). This noise reducing property will be applied in Section 5.2.

Gaussian low-pass filter (frequency domain)

Inverse 2D FFT of Gaussian low-pass filter (spatial domain.)

Figure 3-2 2D Gaussian filter in frequency (left) and spatial (right) domains

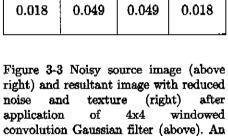

| 0.018 | 0.049 | 0.049 | 0.018 |

|-------|-------|-------|-------|

| 0.049 | 0.134 | 0.134 | 0.049 |

| 0.049 | 0.134 | 0.134 | 0.049 |

| 0.018 | 0.049 | 0.049 | 0.018 |

enlarged region (red box) helps identify

the difference in noise.

## 3.2 FPGA Implementation

Implementing algorithms in an FPGA is very different to writing software code to perform the equivalent task. Although it is possible in theory to design an FPGA layout which executes software code similar to a CPU, this would be extremely inefficient compared to the real CPU. The strength of the FPGA lies in the ability of the designer to construct logic that is highly specialised to a particular task. An FPGA circuit necessarily operates at a slower clock rate compared to a hard-wired circuit implemented in the same technology, but the FPGA can be hardwired to perform many steps of a repetitive task

simultaneously, and gain a performance advantage through parallelism. The advantage of doing this with an FPGA over a regular ASIC or CMOS design is the ability to reprogram a new layout, allowing one chip to perform multiple tasks, minimizing low volume (< 100,000 unit) design and production costs, and maximising flexibility.

From an FPGA's perspective, the most difficult aspect of the convolution algorithm is the multiplication. For each output pixel, for which the total number is similar to the number of input pixels, The number of multiplications is  $W_1W_2$ , where  $W_1$  and  $W_2$  are the window width and height respectively. Each single multiplier would take up an enormous portion of the FPGA logic, and operate at a slow speed. Fortunately to solve this, Xilinx provide 20 dedicated multipliers on the Spartan3E chip utilized. These multipliers are a precious resource, and since they can perform a multiplication every clock cycle for a 50MHz system, a circuit for calculating convolutions using only a single multiplier, and taking W<sub>1</sub>W<sub>2</sub> clock cycles per multiplication was devised. The initial implementation uses a window size of 4x4, as memory performance suffers dramatically if the number of block RAMs in the hardwired pre-fetch cache is not at least equal to the number of lines of the window plus one divided by 5, rounding up. Since both block RAMs and multipliers exist in the same quantity on most Xilinx chip, this symmetry in utilisation for each convolution operator makes sense. Convolution can be speeded up further by adding multiple convolutions in parallel on different image locations. Convolutions of larger window sizes can be achieved by summing the results of smaller convolutions. Combining techniques reduces variability these the convolution implementations necessary.

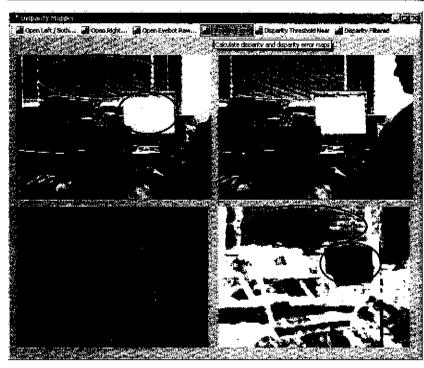

Figure 3-4 FPGA resource utilisation for 4x4 convolution block.

One difficulty with implementing an algorithm in an FPGA context is the inability to run the chip in any kind of debug mode. Combined with the complexity of adding simple debugging IO to the design, locating bugs becomes extremely time consuming. To address this, special code was written to the Xilinx VHDL logic and timing level simulators to external C++ applications. This code uses only standard VHDL and C++ libraries, and so should work with any development simulator/programming environment combination. In addition, a GUI for analysis the convolution algorithm under different conditions was implemented.

Figure 3-5 C++ test harness with .NET UI.

### 3.2.1 Performance Results

The performance results for the convolution algorithm are quite predictable. As work on the FPGA peripherals could not begin until the PCB was completed, time did not allow for the testing of convolution algorithms on the real FPGA. Still the hard-wired logic has predictable performance characteristics, from which estimates were derived (Figure 2-5).

Figure 3-6 Performance estimates for full real-time convolution system running on FPGA, with comparison to PC performance (Reference algorithm running on a 1.83GHz Intel Core Duo, binaries built with Microsoft Visual Studio 8.

# Chapter 4

# Geometry of Depth Perception

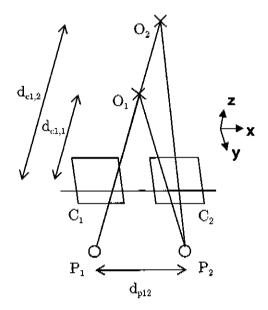

The Eyebot M6 platform has a standard arrangement of two cameras facing the same direction, spaced a small distance apart. This arrangement, similar to the human visual system, gives the platform stereo-vision. The key benefit of this arrangement is the potential ability to perceive depth. The determination of depth from multiple, two-dimensional images can often be achieved through comparison of the varying relative locations of points visible in both images. The initial steps in the development of an implementation of this technology on the Eyebot platform will be discussed.

Stereo-vision algorithms require large amounts of computation to achieve good results. It is not expected that a satisfactory real-time, general purpose stereo vision system can be implemented using the general purpose CPU of the new eyebot platform. Instead the focus of this discussion will be the selection and optimisation of algorithms in such a way as to fit an implementation on the platform's Spartan 3E FPGA. Consideration will be given to the utilisation level of the specific resources available on this FPGA at every stage. The goal is to derive a stereo algorithm which can be implemented so as to provide several frames of depth information per second, whilst offering the maximum information possible.

### 4.1 Projective Geometry

The first step in deriving a sterco algorithm is to consider the geometry involved, and a method of relating the 2D image data to the true 3D scene. To do this, the geometry of the camera is considered to be like that of a pin-hole camera (cameras that introduce no significant lens distortion to the image.) Understanding this simplified relationship mathematically begins by defining the projection matrix K which converts between a coordinate (u,v) in 2D image space and a coordinate (x,y,z) in 3D space. The explanation which follows has in part been adapted from [12]. Equation (4.1) shows the construction of a matrix from the following parameters:

f : focal length

(uo,vo) : intersection of Z axis with image plane

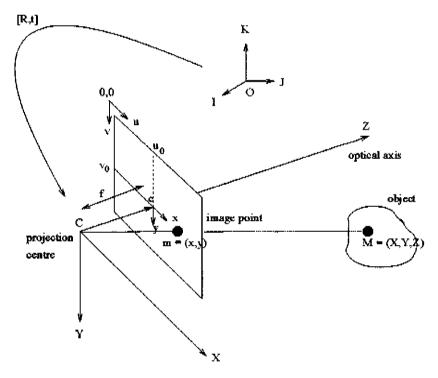

The geometry for this situation is illustrated in Figure 4-1.

Note that square pixels, as found almost exclusively on modern cameras, have been assumed here. For rectangular pixels with different widths and heights two separate focal lengths fu and fv would be required.

$$K = \begin{bmatrix} f & 0 & u_0 & 0 \\ 0 & f & v_0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

(4.1)

Figure 4-1 Basic projective geometry[12]

## 4.2 Full Pinhole Camera Geometry

The projection matrix K requires the camera to be at a fixed position in world space, which is obviously incompatible with the notion of two cameras viewing the same scene. To generalize to multiple cameras, a calibration matrix C can be constructed which includes an arbitrary transformation of the camera relative to world coordinates. The additional parameters for this matrix, shown in equation (4.2) are:

R : 3x3 rotation matrix t : 3x1 translation vector

$$T = \begin{bmatrix} t & R \\ 0_3^t & 1 \end{bmatrix} \tag{4.2}$$

$$C = KT (4.3)$$

This relationship for a pair of cameras viewing the same 3D scene is expressed in equation (4.4).

$$C_{1}\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} s_{1}u_{1} \\ s_{1}v_{1} \\ s_{1} \end{bmatrix} \qquad C_{2}\begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix} = \begin{bmatrix} s_{2}u_{2} \\ s_{2}v_{2} \\ s_{2} \end{bmatrix}$$

$$(4.4)$$

### 4.3 Epipolar Geometry

The geometry for two pinhole cameras as derived in 4.2 is illustrated in Figure 4-1. There are two crucial points to be made at this stage. The first is that, for each point seen by one camera, there are infinitely many object positions which share the relationship so that the lines connecting them to the camera's projection centre overlap, and therefore share the same image coordinate. The second is that all of these object positions project to different points in the second image (ignoring the lack of non-discrete pixel locations), and all of these points form a single line on which lies the epipole (The point where the baseline intersects the image plane.) This is the well known epipolar constraint that reduces depth searching from a 2D to 1D problem.

## 4.4 Co-planar Images

Figure 4-2 Geometry for a pair of cameras aligned to give parallel image planes

If two pinhole cameras are lined up such that they share a common image plane, then the epipoles will now be at infinity. Since they only meet at infinity, all epipolar lines will be parallel and horizontal[13]. The projective geometry for this situation is illustrated in Figure 4-2. If the x and y axis are parallel to the image planes of the cameras, objects O1 and O2 are spaced in

between the two cameras on the x-axis or have the identical y coordinates, and both objects project to the same coordinate in the left hand camera's image, then the corresponding projected points in the right image will have the same y coordinate as in the left, and therefore be on the same scanline.

### 4.5 Practical Rectification

Disparity mapping algorithms, as discussed in Chapter 5, calculate disparity by searching image sets for matching regions and calculating distances between them. It will be shown that, if it is possible, using the techniques discussed in this chapter, to constrain all equivalent points to lie on epi-polar lines that are parallel in the source images, then it will be possible to compute high quality disparity maps in real-time on the M6 platform. This becomes possible because the search space for disparity maps is reduced substantially, and the use of rectangular windows which can have their SAD computation optimised, rather than circular windows, is possible.

Repetitive Plain

Table 4-1 Stereo source images captured with a single camera moved by hand, along with SAD disparity map and minimum window error. It can be seen that the SAD algorithm, as discussed later, does not require perfect alignment. In particular many of the regions with poor accuracy are due to deficiencies in the SAD algorithm irrespective of rectification, which will be covered in more detail in the later chapters.

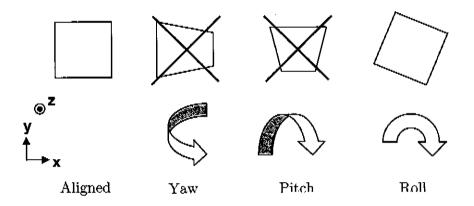

Two cameras that look similar physically (same make, model) may not, when their casings are lined up side by side facing the same direction, give a good approximation of co-planar images. Large stereo systems typically employ a biprism setup[14], where a single sensor is used to capture the image data, and a special lens system with a prism focuses views from two disparate positions onto this sensor. The bi-prism system ensures that the stereo image pair will be coplanar regardless of the small variation in the position and orientation of the capture surface in different cameras. The optical portions of the camera may introduce a rotation with unacceptable pitch and yaw components. In our testing of three Cameras of identical make and model (OV6630) we found that two had only a roll and translation as the significant misalignment components, while the third had pitch and yaw significant enough to prevent the affine

transform from recovering a suitably rectified pair. Therefore it is necessary to be cautious when assuming that a simpler transformation will be sufficient based off the external geometry of the cameras utilised.

### 4.5.1 Affine Transform Rectification

If we restrict ourselves to roll rotations, x translations and y translations, then the transform required on each coordinate in the second image relative to the first is independent of the depth. A single transformation can then be found and applied to the second image only. This transformation will remain constant between frames as long as the relative alignment of the cameras is unchanged.

Figure 4-3 A comparison of the different components of relative rotation for two camera images, including the depth skew from the yaw and pitch components.

This transformation would be at most half as computationally complex as the full calibration method. If the roll rotation is within a few degrees then it is possible to allocate sufficient block RAM within the FPGA to only require reading each pixel from the SRAM once during the transform. In this case the impact of the transformation on the performance of other components is greatly reduced.

It is likely that, with further testing, it can be demonstrated that the Eyebot M6 can give useable quality depth information from its stereo cameras using

only this level of rectification. The yaw and pitch will not be significant with most camera pairs as the physical geometry always aligns them correctly externally. This would make a real-time (multiple frames per second) implementation feasible.

#### 4.5.2 General Stereo Rectification

There are four steps required for rectification with complete generality with respect to camera position[15].

- Rotate the left camera so that the epipole goes to infinity along the horizontal axis (i.e. the left image plane becomes parallel to the baseline of the system).

- Apply the same rotation to the right camera to recover the original geometry.

- Rotate the right camera by R.

- Adjust the scale in both camera reference frames.

There are two problems with supporting this general case on an embedded platform. The first is the complexity of the full transformation, which is significant not only because it requires extremely high performance multiplication, but also because it has unpredictable memory access characteristics which do not fit well with the FPGA user designed cacheing model. If this level of rectification is required, it may be necessary to involve the CPU, which will almost certainly bring performance down to below one frame per second.

# Chapter 5

# Real Time Disparity Mapping

## 5.1 Disparity Mapping Methods